- #Parallel to serial converter using mux and flip flops how to#

- #Parallel to serial converter using mux and flip flops 64 bits#

- #Parallel to serial converter using mux and flip flops code#

- #Parallel to serial converter using mux and flip flops download#

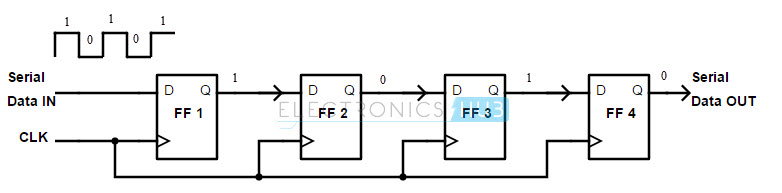

The next picture shows a circuit of a 4-bit serial shift register designed to shift right. The JK flip-flop is very flexible and therefore allows simpler circuit designs.

#Parallel to serial converter using mux and flip flops code#

of dff is begin - Your VHDL code defining the model goes here output: process. Using different VHDL methods to describe the Flip-Flops Investigating registers. Designing: The function characteristics of the 74F194, 4-bit bidirectional shift register is shown in the function.

by running several shift registers of the same bit-length in parallel. shifting in the data present at its input and shifting out the last bit in the. To develop a VHDL code for Universal Shift Register. QC finally goes high at clock t4 due to the high fed to D from the previous stage. Type JK FFs cascaded Q to J, Q' to K with clocks in parallel to yield an.

#Parallel to serial converter using mux and flip flops 64 bits#

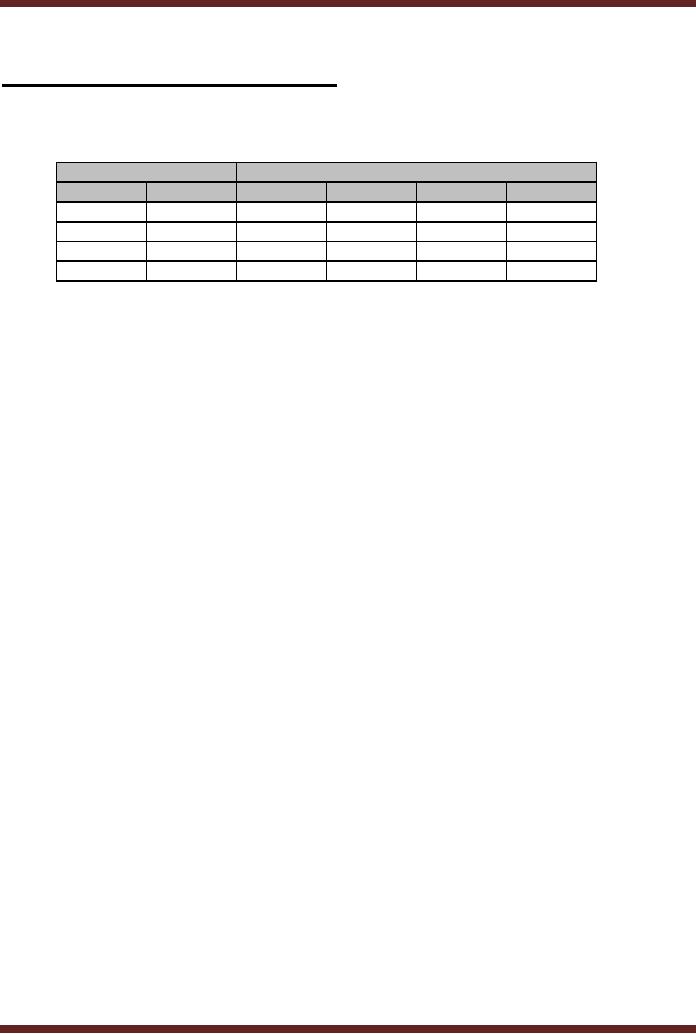

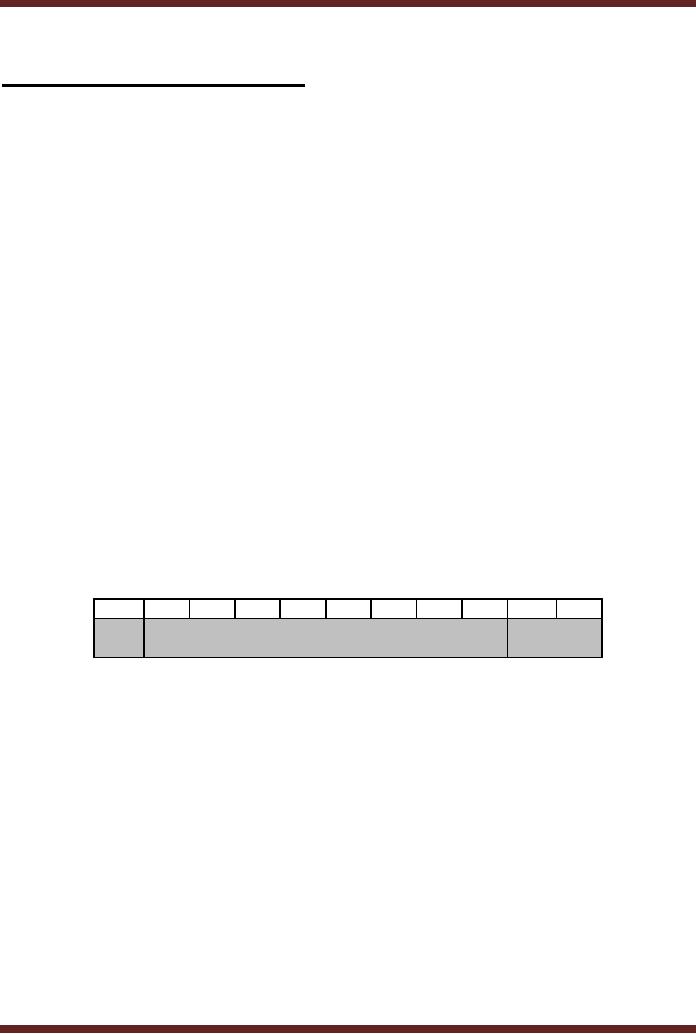

A serial-in, serial-out shift register may be one to 64 bits in length, longer if registers or. Serial-in, serial-out shift registers delay data by one clock time for each stage. are implementing a program for Serial in Serial Out (SISO) Shift Register in VHDL Language. 6 min - Uploaded by Beginners Point Shruti Jain. Parallel Load, Serial IN, and Serial OUT 9-28 9.4.7 8-bit Shift-Left Register. Shift Register with an Enable Input 9-23 9.4.5 VHDL Code for a 4-bit Parallel. Description of JK Flip-Flop 9-14 9.3.11 Behavioral Description of JK Flip-Flop using. Issuu is a digital publishing platform that makes it simple to publish magazines, catalogs, newspapers, books, and more online.

#Parallel to serial converter using mux and flip flops how to#

How to write verilog code for 16 bit 2's complement serial subtrator. Design of Serial IN - Serial OUT Shift Register using D Flip Flop. 06:14 Naresh Singh 4 comments Email This BlogThis! Share to Twitter Share to Facebook. Design of JK Flip Flop using Behavior Modeling Style - Output Waveform : JK. Design of JK Flip Flop using Behavior Modeling Sty. Design of 4 bit Serial IN - Serial OUT Shift Register using Behavior Modeling Style (VHDL Code). Design of 3 : 8 Decoder Using When-Else Statement (VHDL Code). So far, here is what I have: Now, the code itself compiles. Hello, I'm trying to create a simple 4-bit parallel in and serial out shift register. In general a shift register is characterized by the following control and. The bits are then individually shifted out, one bit per clock cycle, on the serial output line.

#Parallel to serial converter using mux and flip flops download#

Vhdl Code for Serial in Serial Out Shift Register Using Behavioral Modelling - Free download as Word Doc (.doc /. The register should have one data input sin (serial in) and one. a) Right Shift Register: Construct a 4-bit shift register using D Flip-Flops that shifts its content to the right. b) JK Flip-Flop in VHDL: The VHDL code that describes a D Flip-Flop is given in the. Shift register vhdl code, shift register vhdl code siso, shift register vhdl code and testbench, shift register vhdl code 8 bit, shift register vhdl code 4 bit, shift register vhdl code with test bench, universal shift register vhdl code, parallel in serial out shift register vhdl code, linear feedback shift register vhdl code, bidirectional shift register vhdl code, piso shift register vhdl code, pipo shift register vhdl code, left shift register vhdl codeĤ Bit Serial In Serial Out Shift Register Vhdl Code For A Jk > DOWNLOADĭraw the corresponding timing diagrams for the two resulting output.

0 kommentar(er)

0 kommentar(er)